### intel CD1400 UXART Serial/Parallel Controller

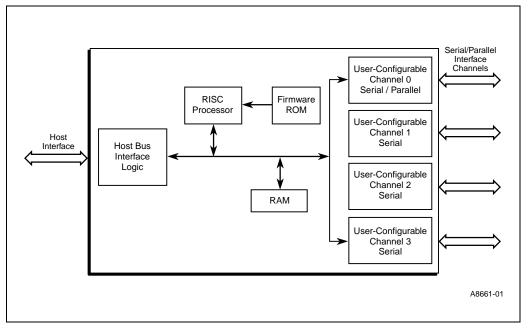

The CD1400 is a flexible asynchronous receiver/transmitter with four full-duplex serial channels, or three full-duplex serial channels and one high-speed bidirectional parallel channel. With optional special character processing capabilities, it is especially well-suited for UNIX applications. The CD1400 is fabricated in an advanced-CMOS process and operates on a system clock of up to 60 MHz. Packaged in a 100-pin MQFP, its high throughput, low-power consumption and high level of integration permit system designs with minimum part-count, maximum performance and maximum reliability.

*Note:* This document applies to the CD1400 Revision J or later device.

*Note:* The CD1400 is only offered in a 100-pin MQFP package.

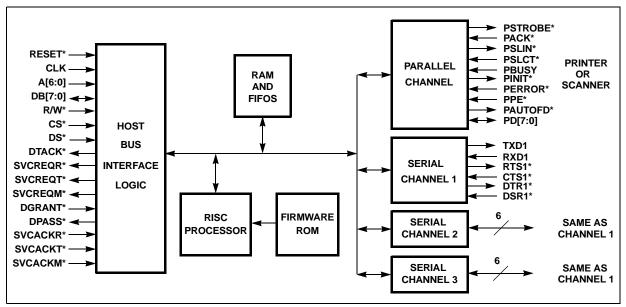

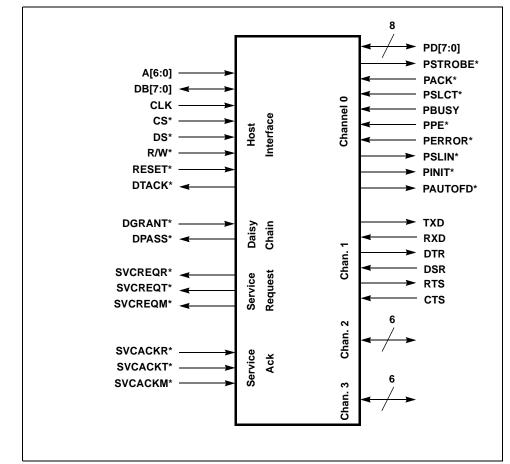

#### Figure 1. Functional Block Diagram

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The CD1400 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Feat       | ures                                                                                                                                                                                                                                                     | 9                          |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|     | 1.1        | Asynchronous Features                                                                                                                                                                                                                                    |                            |

|     | 1.2        | Parallel Features                                                                                                                                                                                                                                        |                            |

| 2.0 | Con        | figuration Examples                                                                                                                                                                                                                                      | 10                         |

| 3.0 | Desi       | ign Considerations                                                                                                                                                                                                                                       | 10                         |

|     | 3.1        | Pin Differences                                                                                                                                                                                                                                          | 10                         |

| 4.0 | Con        | ventions                                                                                                                                                                                                                                                 | 11                         |

|     | 4.1<br>4.2 | Abbreviations<br>Acronyms                                                                                                                                                                                                                                |                            |

| 5.0 | Pin l      | Information                                                                                                                                                                                                                                              | 14                         |

|     | 5.1<br>5.2 | Pin Functions - Major Operational Modes<br>Pin List                                                                                                                                                                                                      |                            |

| 6.0 | Regi       | isters                                                                                                                                                                                                                                                   |                            |

|     | 6.1<br>6.2 | CD1400 Register Map<br>Register Definitions                                                                                                                                                                                                              | 23                         |

| 7.0 | Fund       | ctional Description                                                                                                                                                                                                                                      |                            |

|     | 7.1<br>7.2 | Device Architecture<br>Host Interface<br>7.2.1 Host Read Cycles<br>7.2.2 Host Write Cycles                                                                                                                                                               | 29<br>30<br>31<br>31       |

|     | 7.3        | <ul> <li>7.2.3 Host Service Acknowledge Cycles</li> <li>Service Requests</li></ul>                                                                                                                                                                       | 32<br>33<br>36             |

|     | 7.4        | <ul> <li>Serial Data Reception and Transmission</li> <li>7.4.1 Receiver Operation</li> <li>7.4.2 Receiver Timer Operations</li> <li>7.4.3 Receive Exceptions</li> <li>7.4.4 Transmitter Operation</li> <li>7.4.5 Transmitter Timer Operations</li> </ul> | 38<br>40<br>40<br>41<br>42 |

|     | 7.5        | Flow Control         7.5.1       In-Band Flow Control         7.5.2       Out-of-Band Flow Control         7.5.3       Modem Signals and General-Purpose I/O                                                                                             | 45<br>45<br>47<br>48       |

|     | 7.6        | Receive Special Character Processing         7.6.1       UNIX Character Processing         7.6.2       Non-UNIX Receive Special Character Processing                                                                                                     | 51                         |

|     | 7.7        | Transmit Special Character Processing7.7.1Line Terminating Characters7.7.2Embedded Transmit Commands                                                                                                                                                     | 56<br>56                   |

|     |      | 7.7.3 Send Special Character Command                              | 57           |

|-----|------|-------------------------------------------------------------------|--------------|

|     | 7.8  | Baud Rate Generation                                              |              |

|     | 7.9  | Diagnostic Facilities — Loopback                                  |              |

|     | 7.10 | Parallel Channel Operations                                       |              |

|     |      | 7.10.1 Transmit Operation                                         |              |

|     |      | 7.10.2 Receive Operation                                          |              |

|     |      | 7.10.3 Programming Considerations                                 |              |

|     | 7.11 | Hardware Configurations                                           |              |

|     |      | 7.11.1 Interfacing to an Intel Microprocessor-Based System        |              |

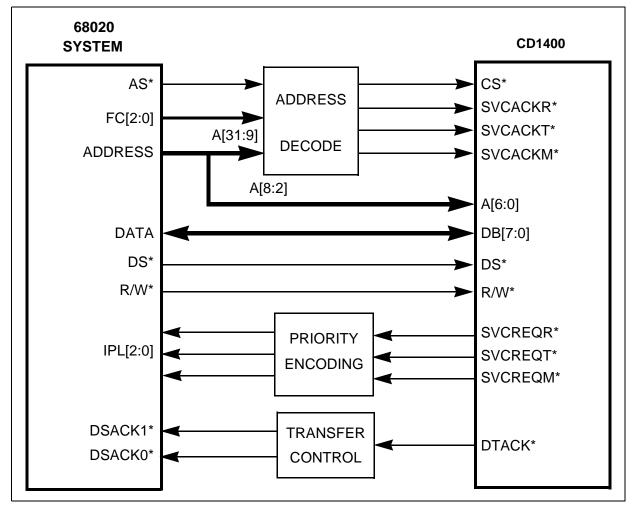

|     |      | 7.11.2 Interfacing to a Motorola* Microprocessor-Based System     |              |

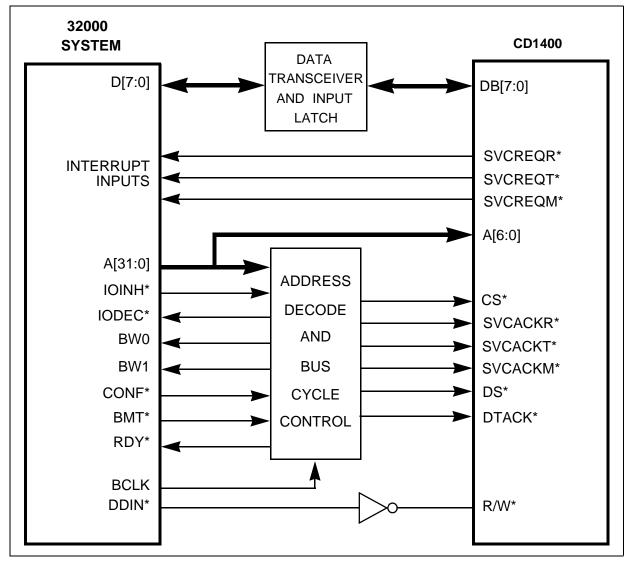

|     |      | 7.11.3 Interfacing to a National Semiconductor* Microprocessor-Ba | ised System. |

|     |      | 67                                                                |              |

| 8.0 | Prog | Jramming                                                          | 71           |

|     | 8.1  | Overview                                                          | 71           |

|     | 8.2  | Initialization                                                    | 71           |

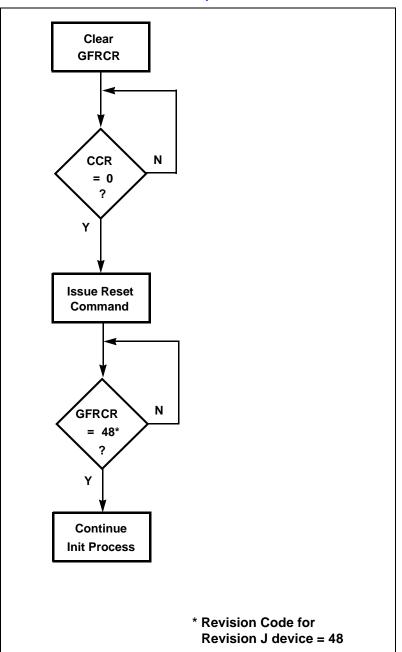

|     |      | 8.2.1 Chip Initialization                                         | 71           |

|     |      | 8.2.2 Global Function Initialization                              | 73           |

|     |      | 8.2.3 Individual Channel Initialization                           | 74           |

|     | 8.3  | Poll Mode Examples                                                | 75           |

|     |      | 8.3.1 Polling Routine Examples                                    |              |

|     | 8.4  | Hardware-Activated Service Examples                               |              |

|     |      | 8.4.1 Receive Service                                             |              |

|     |      | 8.4.2 Transmit Service                                            |              |

|     |      | 8.4.3 Modem Service                                               |              |

|     |      | 8.4.4 Baud Rate Derivation                                        |              |

|     | 8.5  | Baud Rate Tables                                                  |              |

|     | 8.6  | ASCII Code Table                                                  |              |

|     |      | 8.6.1 Hexadecimal — Character                                     |              |

|     |      | 8.6.2 Decimal — Character                                         |              |

| 9.0 | Deta | iled Register Descriptions                                        |              |

|     | 9.1  | Global Registers                                                  |              |

|     |      | 9.1.1 Global Firmware Revision Code (GFRCR)                       |              |

|     |      | 9.1.2 Channel Access Register (CAR)                               |              |

|     |      | 9.1.3 Global Configuration Register (GCR)                         |              |

|     |      | 9.1.4 Service Request Register (SVRR)                             | 90           |

|     |      | 9.1.5 Receive Interrupting Channel Register (RICR)                |              |

|     |      | 9.1.6 Transmit Interrupting Channel Register (TICR)               |              |

|     |      | 9.1.7 Modem Interrupting Channel Register (MICR)                  |              |

|     |      | 9.1.8 Receive Interrupt Register (RIR)                            |              |

|     |      | 9.1.9 Transmit Interrupt Register (TIR)                           |              |

|     |      | 9.1.10 Modem Interrupt Register (MIR)                             |              |

|     |      | 9.1.11 Prescaler Period Register (PPR)                            |              |

|     | 9.2  | Virtual Registers                                                 |              |

|     |      | 9.2.1 Receive Interrupt Vector Register (RIVR)                    |              |

|     |      | 9.2.2 Transmit Interrupt Vector Register (TIVR)                   |              |

|     |      | 9.2.3 Modem Interrupt Vector Register (MIVR)                      |              |

|     |      | 9.2.4 Transmit Data Register (TDR)                                |              |

|     |      | 9.2.5 Receive Data/Status Register (RDSR)                         |              |

|        | 9.2.6    | Receive Data/Status Register (RDSR)                     |     |

|--------|----------|---------------------------------------------------------|-----|

|        | 9.2.7    | Modem Interrupt Status Register (MISR)                  |     |

|        | 9.2.8    | End Of Service Request Register (EOSRR)                 | 98  |

| 9.3    | Channe   | el Registers                                            |     |

|        | 9.3.1    | Local Interrupt Vector Register (LIVR)                  | 99  |

|        | 9.3.2    | Channel Command Register (CCR)                          |     |

|        | 9.3.3    | Service Request Enable Register (SRER)                  | 104 |

| 9.4    | Channe   | el Option Registers                                     | 105 |

|        | 9.4.1    | Channel Option Register 1 (COR1)                        | 105 |

|        | 9.4.2    | Channel Option Register 2 (COR2)                        | 107 |

|        | 9.4.3    | Channel Option Register 3 (COR3) Serial Format          | 108 |

|        | 9.4.4    | Channel Option Register 3 (COR3) Parallel Format        | 108 |

|        | 9.4.5    | Channel Option Register 4 (COR4)                        | 110 |

|        | 9.4.6    | Channel Option Register 5 (COR5)                        | 111 |

|        | 9.4.7    | Channel Control Status Register (CCSR) Serial Format    | 112 |

|        | 9.4.8    | Channel Control Status Register (CCSR) Parallel Format  | 112 |

|        | 9.4.9    | Received Data Count Register (RDCR) Serial Format       | 114 |

|        | 9.4.10   | Received Data Count Register (RDCR) Parallel Format     | 114 |

| 9.5    | Special  | Character Registers                                     | 116 |

|        | 9.5.1    | Special Character Register 1 (SCHR1)                    | 116 |

|        | 9.5.2    | Special Character Register 2 (SCHR2)                    | 116 |

|        | 9.5.3    | Special Character Register 3 (SCHR3)                    | 116 |

|        | 9.5.4    | Special Character Register 4 (SCHR4)                    | 117 |

|        | 9.5.5    | Special Character Range Low (SCRL)                      | 117 |

|        | 9.5.6    | Special Character Range High (SCRH)                     | 117 |

|        | 9.5.7    | LNext Character (LNC)                                   | 118 |

| 9.6    | Modem    | Change Option Registers                                 | 118 |

|        | 9.6.1    | Modem Change Option Register 1 (MCOR1) Serial Format    | 118 |

|        | 9.6.2    | Modem Change Option Register 1 (MCOR1) Parallel Format. | 119 |

|        | 9.6.3    | Modem Change Option Register 2 (MCOR2) Serial Format    | 120 |

|        | 9.6.4    | Modem Change Option Register 2 (MCOR2) Parallel Format. | 120 |

|        | 9.6.5    | Receive Time-out Period Register (RTPR)                 | 121 |

|        | 9.6.6    | Modem Signal Value Register 1 (MSVR1                    | 122 |

|        | 9.6.7    | Modem Signal Value Register 2 (MSVR2)                   | 122 |

|        | 9.6.8    | Printer Signal Value Register (PSVR)                    |     |

|        | 9.6.9    | Receive Baud Rate Period Register (RBPR)                |     |

|        | 9.6.10   | Receive Clock Option Register (RCOR)                    |     |

|        |          | Transmit Baud Rate Period Register (TBPR)               |     |

|        | 9.6.12   | Transmit Clock Option Register (TCOR)                   | 125 |

| Electr | rical Sp | pecifications                                           | 126 |

| 10.1   | Absolut  | te Maximum Ratings                                      | 126 |

| 10.2   |          | mended Operating Conditions                             |     |

| 10.3   |          | ctrical Characteristics                                 |     |

| 10.4   |          | ctrical Characteristics                                 |     |

|        | 10.4.1   | Index of Timing Information                             |     |

|        | -        | Asynchronous Timing                                     |     |

|        |          | Synchronous Timing                                      |     |

|        |          | Parallel Port Timing Specifications                     |     |

|        |          |                                                         |     |

10.0

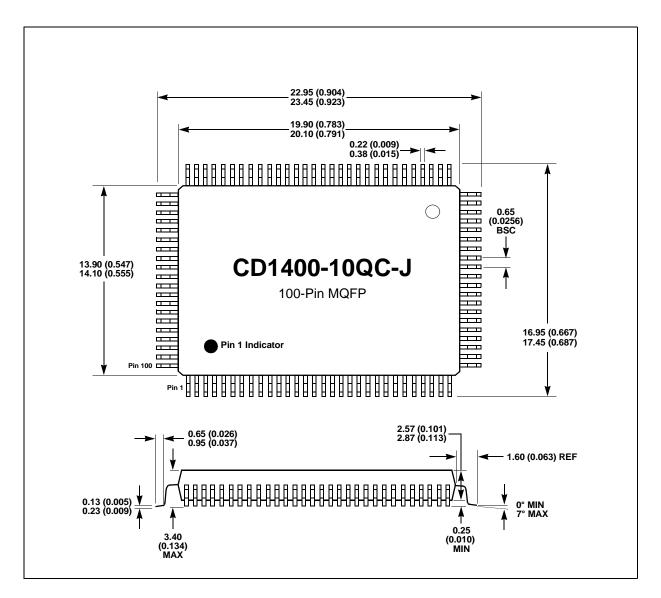

| 11.0 | Package Specifications            |     |

|------|-----------------------------------|-----|

|      | 11.1 100-Pin MQFP (JEDEC) Package |     |

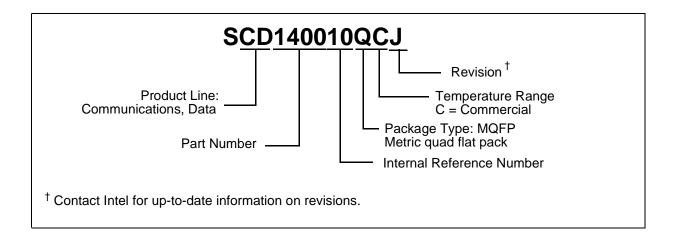

| 12.0 | Ordering Information              |     |

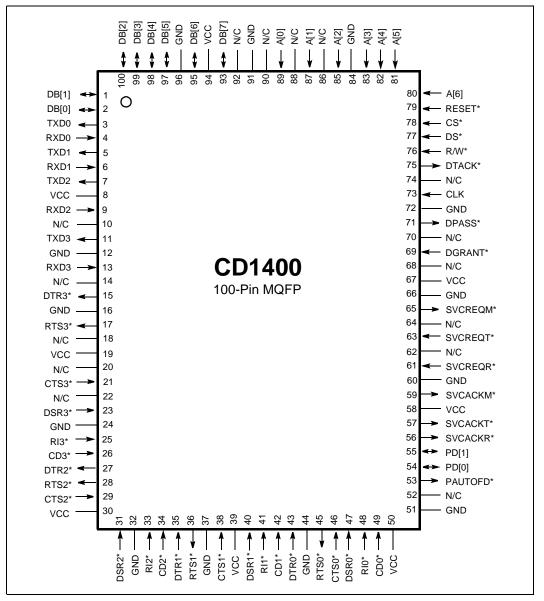

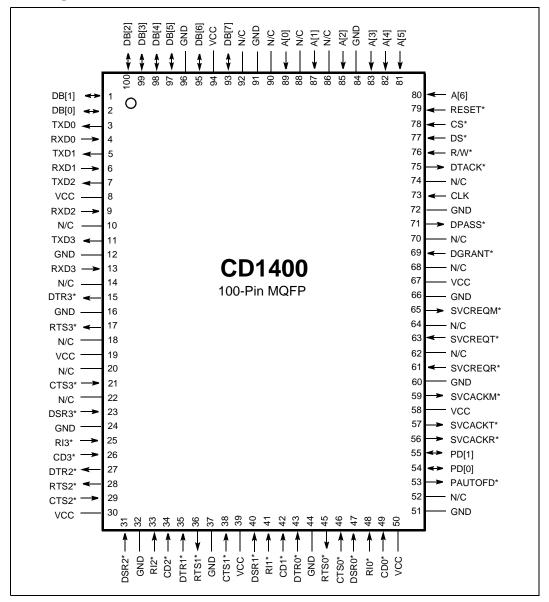

|      | 12.1 Pin Diagram — 100-Pin MQFP   |     |

| 13.0 | Quick Reference                   | 141 |

|      | 13.1 CD1400 Register Map          | 141 |

### **Figures**

| 1  | Workstation: Printer, Keyboard, Mouse and Modem Ports  | 12  |

|----|--------------------------------------------------------|-----|

| 2  | Three Serial Ports and One Bidirectional Parallel Port | 13  |

| 3  | Four Full-Modem Ports                                  | 13  |

| 4  | Pin Diagram — CD1400                                   |     |

| 5  | Pin Functions — Four Serial Channel Mode               | 15  |

| 6  | Pin Functions — Three Serial/One Parallel Channel Mode | 16  |

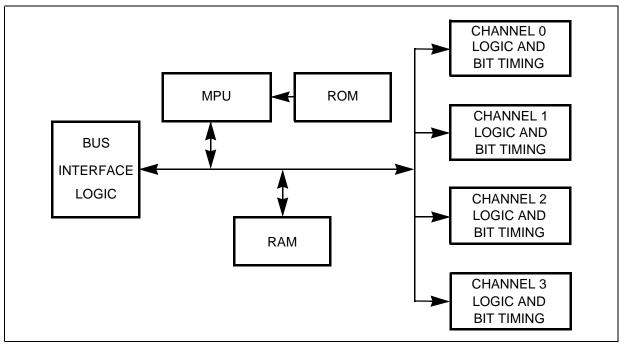

| 7  | CD1400 Functional Block Diagram                        | 29  |

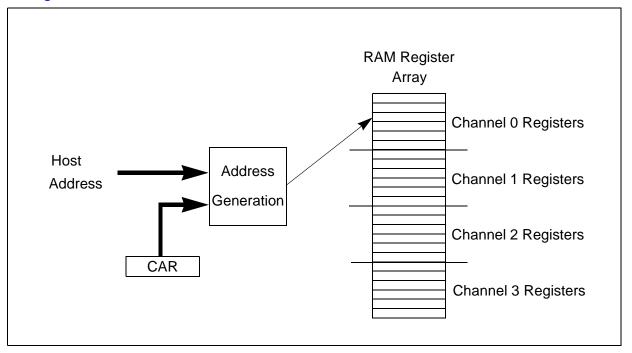

| 8  | Internal Address Generation                            | 31  |

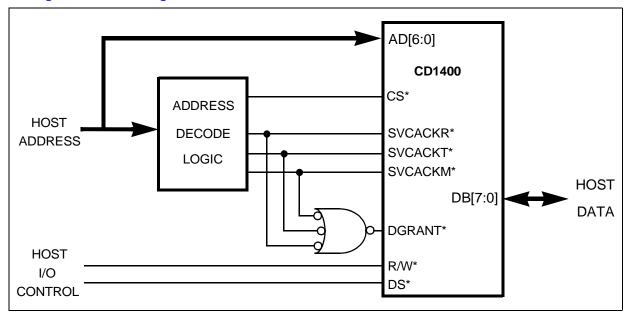

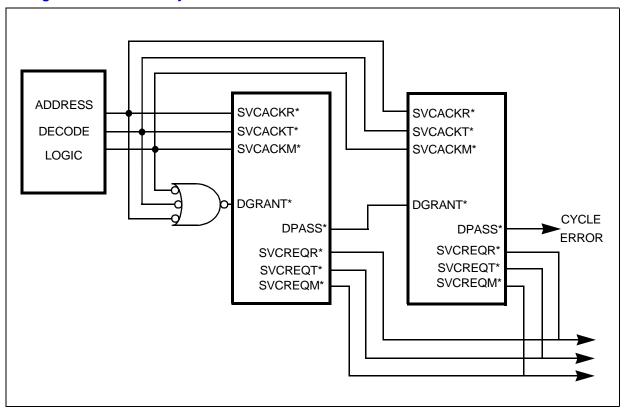

| 9  | Control Signal Generation                              | 34  |

| 10 | CD1400 Daisy-Chain Connections                         |     |

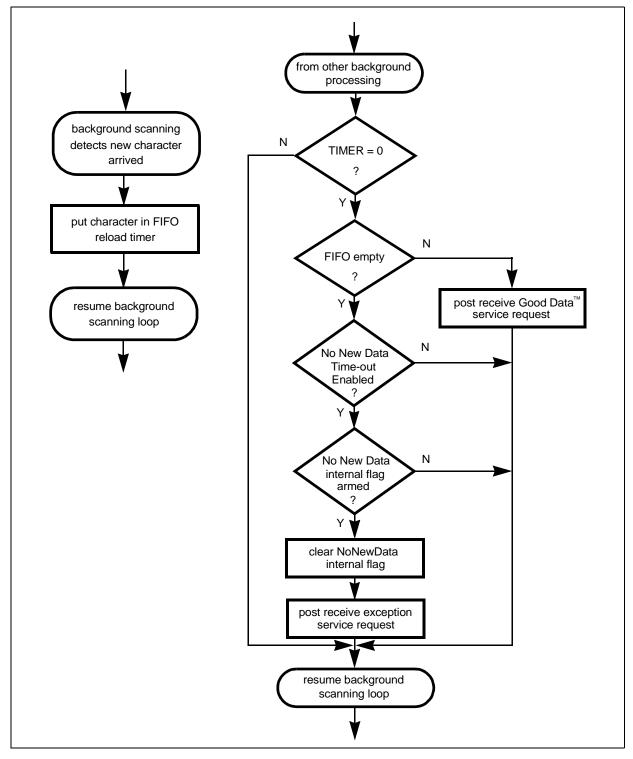

| 11 | FIFO Timer Processing                                  | 44  |

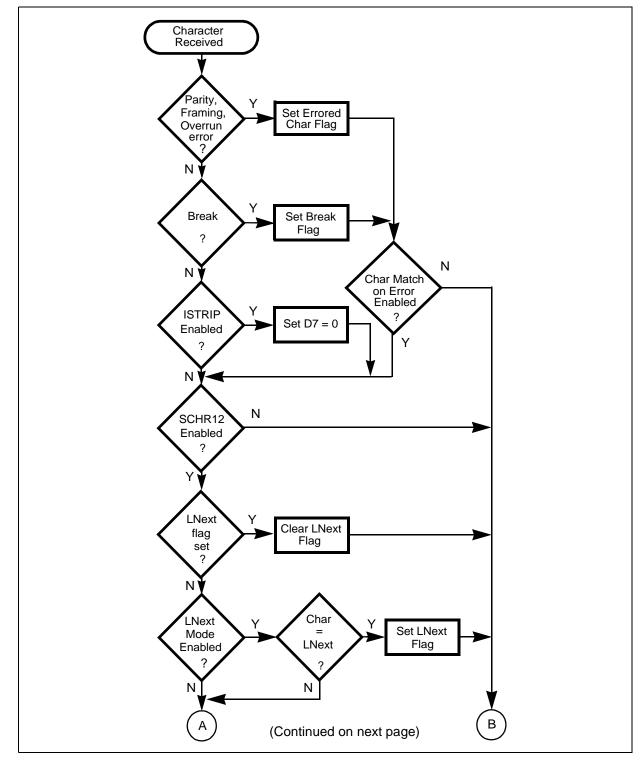

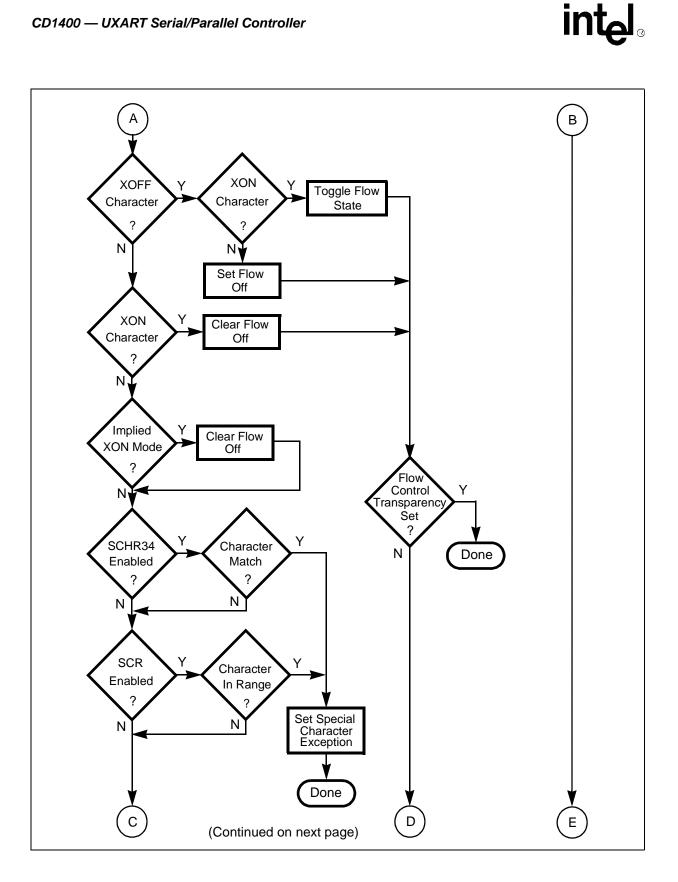

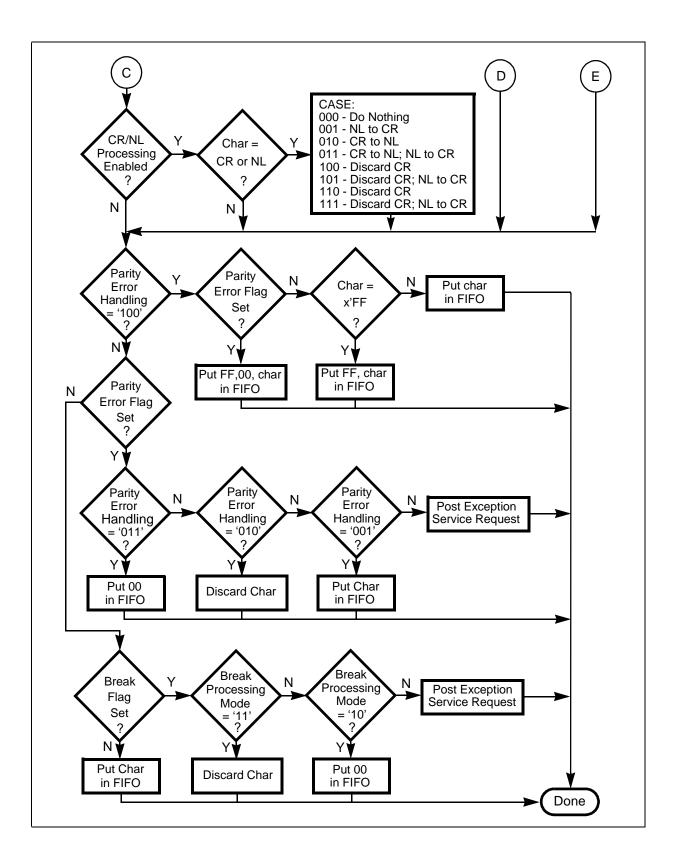

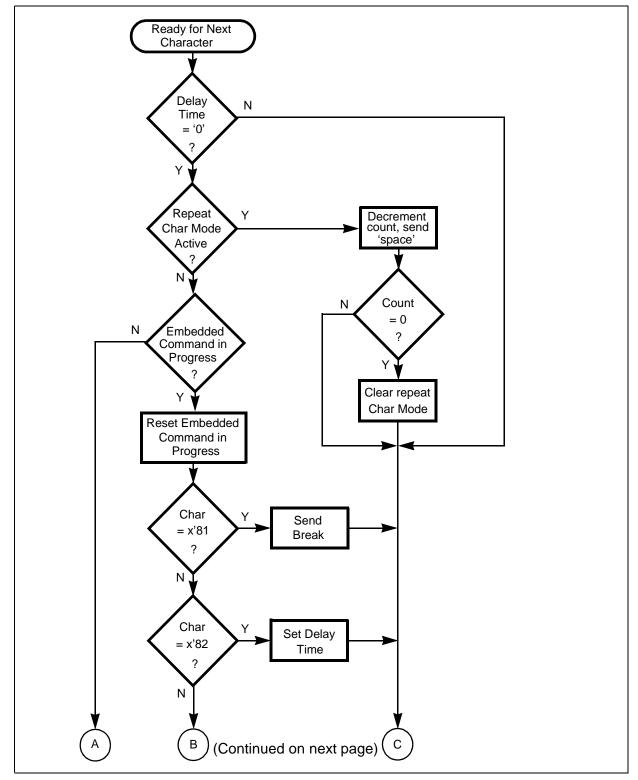

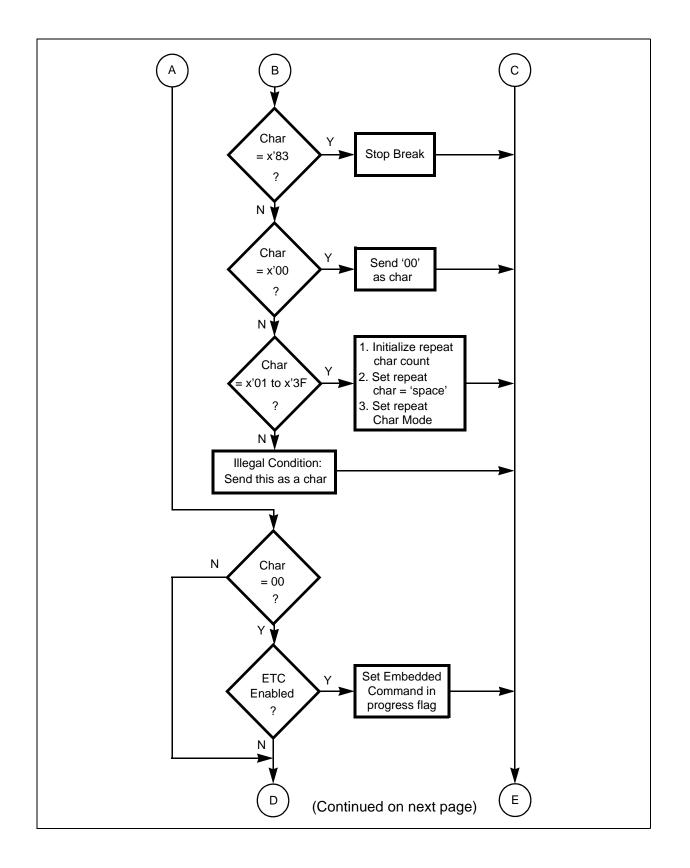

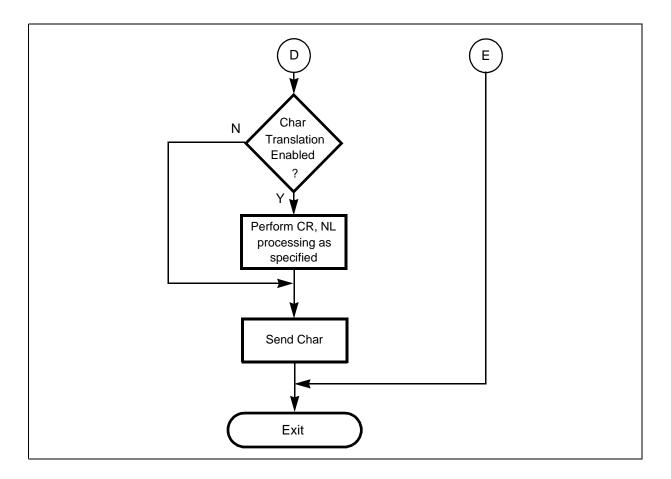

| 12 | CD1400 Receive Character Processing                    | 53  |

| 13 | CD1400 Transmit Character Processing                   | 59  |

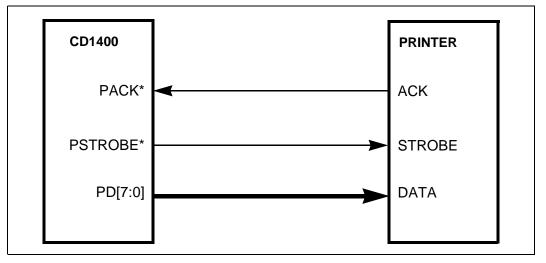

| 14 | CD1400 Parallel Data Transmit Connections              |     |

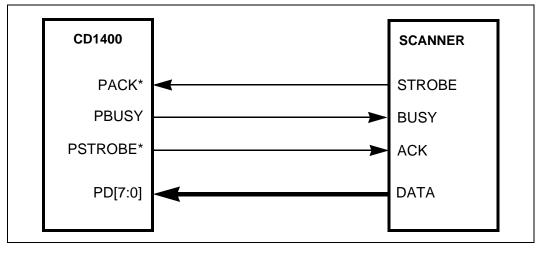

| 15 | CD1400 Parallel Data Receive Connections               | 65  |

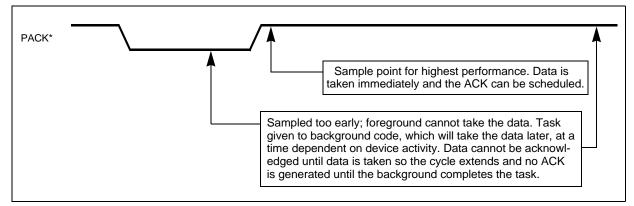

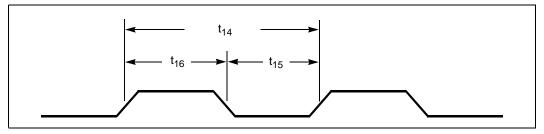

| 16 | Relationship between RCOR/RBPR and PACK* Pulse         | 66  |

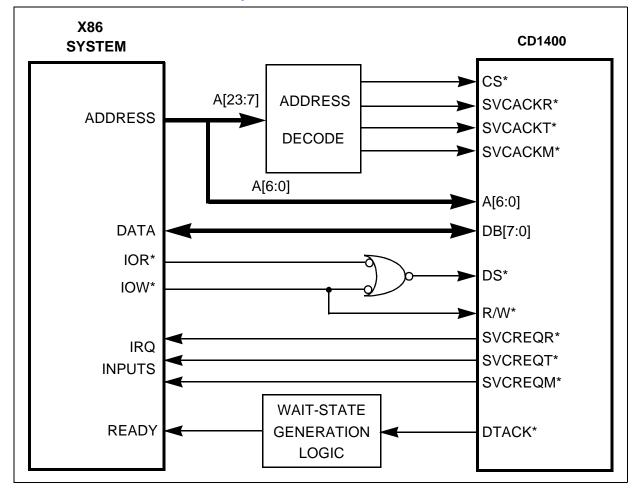

| 17 | Intel, 80x86 Family Interface                          | 68  |

| 18 | Motorola* 68020 Interface                              | 69  |

| 19 | National* 32000 Interface                              |     |

| 20 | CD1400 Master Initialization Sequence                  | 73  |

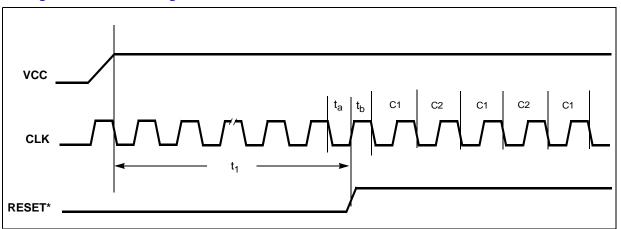

| 21 | Reset Timing                                           | 129 |

| 22 | Clock Timing                                           |     |

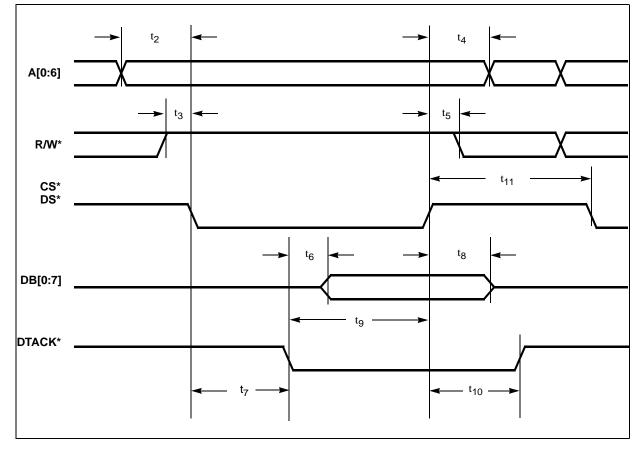

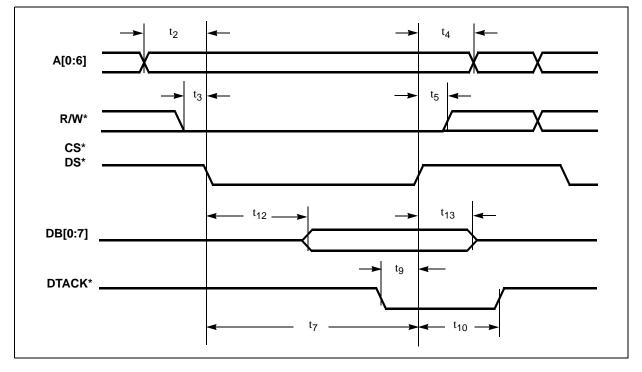

| 23 | Asynchronous Read Cycle Timing                         | 130 |

| 24 | Asynchronous Write Cycle Timing                        |     |

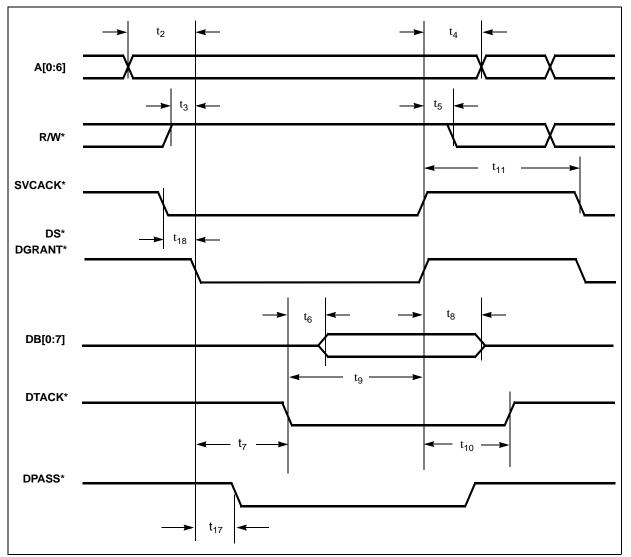

| 25 | Asynchronous Service Acknowledge Cycle Timing          | 132 |

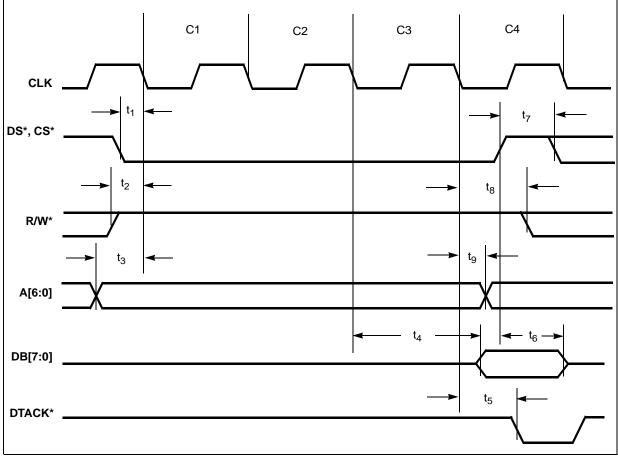

| 26 | Synchronous Read Cycle Timing                          | 133 |

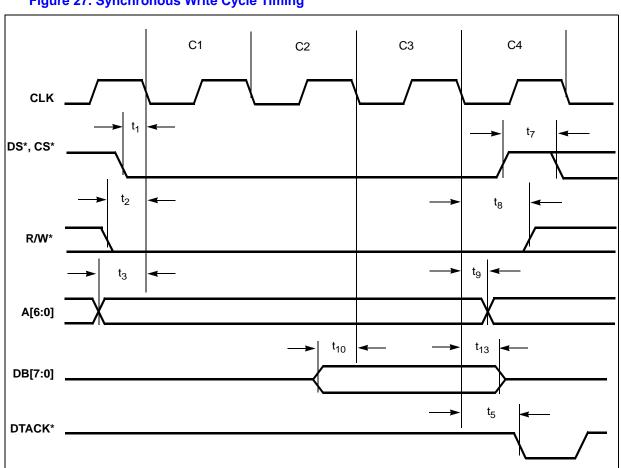

| 27 | Synchronous Write Cycle Timing                         |     |

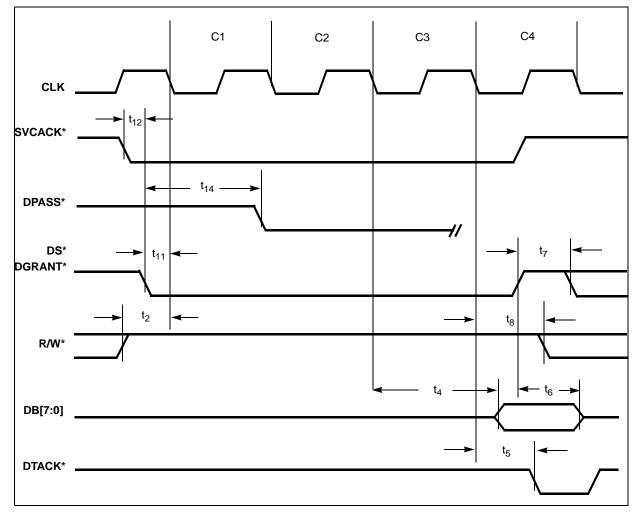

| 28 | Synchronous Service Acknowledge Cycle Timing           | 135 |

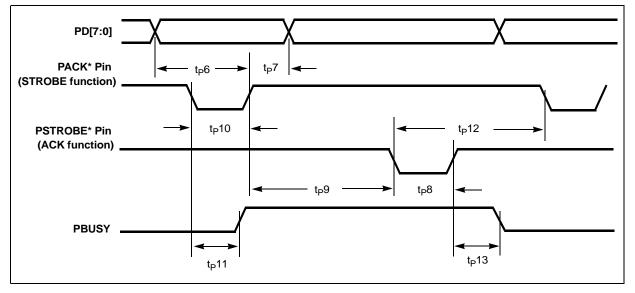

| 29 | Parallel Port Transmit Timing                          |     |

| 30 | Parallel Port Receive Timing                           | 137 |

| 31 | Pin Diagram — 100-Pin MQFP                             | 140 |

|    |                                                        |     |

### Tables

| 1  | General                                               | 16  |

|----|-------------------------------------------------------|-----|

| 2  | Microprocessor Interface                              | 17  |

| 3  | Service Request Interface                             | 17  |

| 4  | Communication Interface                               | 17  |

| 5  | Miscellaneous                                         |     |

| 6  | Pin Descriptions                                      | 19  |

| 7  | Global Registers                                      | 23  |

| 8  | Virtual Registers                                     |     |

| 9  | Channel Registers                                     | 23  |

| 10 | Global Registers                                      | 24  |

| 11 | Virtual Registers                                     | 25  |

| 12 | Channel Registers                                     |     |

| 13 | Modem Registers                                       | 27  |

| 14 | Baud Rate Constants, CLK = 60 MHz                     |     |

| 15 | Baud Rate Constants, CLK = 25 MHz                     |     |

| 16 | Baud Rate Constants, CLK = 20.2752 MHz                | 85  |

| 17 | Receive/Transmit/Modem Interrupting Channel Registers | 91  |

| 18 | Receive/Transmit/Modem Interrupt Vector Registers     | 95  |

| 19 | Receive Data/Status Register                          |     |

| 20 | Global Registers                                      | 141 |

| 21 | Virtual Registers                                     | 141 |

| 22 | Channel Registers                                     |     |

| 23 | Bit Definitions                                       | 142 |

|    |                                                       |     |

### **Revision History**

| Revision | Date     | Description      |

|----------|----------|------------------|

| 1.0      | May 2001 | Initial release. |

### 1.0 Features

#### 1.1 Asynchronous Features

- Software-programmable serial data rates up to 230.4 kbps, full-duplex

- *Note:* A minimum clock frequency of 60 MHz is required to run all four serial channels at a 230.4-kbps data rate. Refer to the AC characteristics ("Electrical Specifications" on page 126) for complete information on device timing.

- Twelve bytes of FIFO for each transmitter and each receiver, with programmable threshold for receive-FIFO-interrupt generation

- Improved interrupt schemes: Good Data\* interrupts eliminate the need for character status check

- Independent bit rate selection for transmit and receive on each channel

- User-programmable and automatic flow control modes for the serial channels:

- In-band (software) flow control via single character (XON/XOFF)

- Out-of-band (hardware) flow control via RTS/CTS and DTR/DSR

- Special character recognition and generation

- Special character processing, particularly useful for UNIX-line-driver applications, optionally handled automatically by the CD1400

- Automatic expansion of NL to CR-NL

- Supports LNEXT and ISTRIP

- Ignore Break

- UNIX parity handling options: Character removed from stream Passed as Good Data<sup>™</sup> Replaced with null (00 hex) Preceded with FF-00 hex

- Passed as is with exception flagged

- Line break detection (start and end) and generation, with programmable choice of response and data pattern to the host

- Insertion of transmit delays in data stream

- One timer per channel for receive data time-out interrupt

- Six modem control signals-per-channel (DTRDSR, RTS, CTS, CD, RI); CD and RI Signals not available if using the parallel channel

- Local and Remote Maintenance Loopback Modes

- Five to eight data bits per character plus optional parity

- Odd, even, no, or forced parity

- 1, 1.5, or 2 Stop bits

#### 1.2 Parallel Features

- Parallel data rates up to 105-Kbytes/sec. receive and 32-Kbytes/sec. transmit

- Thirty-byte FIFO

- Programmable strobe pulse widths

- Automatic generation and recognition of handshake control signals (STROBE, ACK, BUSY)

- Compatible with Centronics\*-interface specifications

- New bits provided to increase parallel signal width

#### 2.0 Configuration Examples

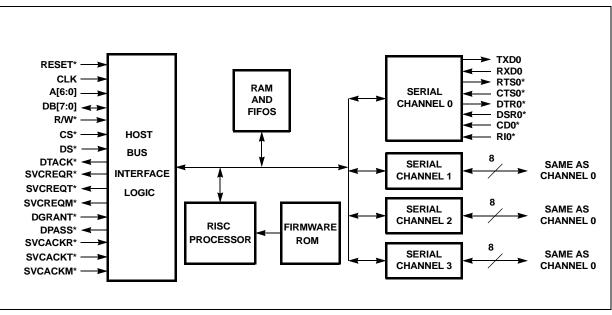

Figure 1 on page 12 through Figure 3 on page 13 are functional block diagrams of three possible configurations that can be implemented with the CD1400. The first is a typical workstation with printer, mouse, keyboard and modem ports, a mode that includes a single parallel port and three serial channels with modem control; Figure 2 illustrates one channel with complete bidirectional modem control and three channels with partial modem control; Figure 3 shows a quad serial mode of four channels with complete modem control. All modes of operation are software-programmable through Control registers within the CD1400.

#### 3.0 Design Considerations

The CD1400 Revision J is a higher speed version of the CD1400 Revision G. The CD1400 Revision J is *only* available in a 100-pin MQFP package.

It is recommended that the CD1400 Revision J be used for any new designs. Please note that to achieve the high data rates, a 60-MHz clock is required. Please refer to the pin differences between the CD1400 Revision G and J.

#### 3.1 Pin Differences

| Feature              | CD1400 Revision J | CD1400 Revision G |

|----------------------|-------------------|-------------------|

| Package              | 100-pin MQFP      | 100-pin MQFP      |

| System clock         | 60 MHz 25 MHz     |                   |

| Maximum bit rates    | 230.4 kbps        | 115.2 kbps        |

| Ground pins          | 13                | 4                 |

| V <sub>CC</sub> pins | 8                 | 3                 |

| No-connect pins      | 15                | 29                |

#### Notes:

- 1. Some of the no-connect pins on the CD1400 Revision G (100-pin MQFP) were converted to additional V<sub>CC</sub> and ground pins on the CD1400 Revision J (please refer to the "Pin List" on page 16 for details).

- 2. The CD1400 Revision G part does not work in a Revision J layout. The Revision G noconnect pins must be left as true no-connect pins and cannot be connected to  $V_{CC}$  or Ground.

- 3. To achieve the high data rates, a 60-MHz system clock is required. However, it is not possible to achieve some low bit rates based on a 60-MHz clock (a lower system clock is required). Refer to "Baud Rate Tables" on page 84 for bit-rate programming constraints.

Higher clock rates produce shorter PSTROBE\* signal pulse widths, so when Channel 0 is programmed as a parallel port, similar limitations must also be considered (see "Parallel Channel Operations" on page 62 for PSTROBE\* pulse-width programming constraints).

#### 4.0 Conventions

#### 4.1 Abbreviations

| Symbol               | Units of measure                  |  |

|----------------------|-----------------------------------|--|

| °C                   | degree Celsius                    |  |

| μF                   | microfarad                        |  |

| μs                   | microsecond (1,000 nanoseconds)   |  |

| Hz                   | hertz (cycle per second)          |  |

| Kbit                 | kilobit (1,024 bits)              |  |

| kbps<br>kbits/second | kilobit (1,000 bits) per second   |  |

| Kbyte                | kilobyte (1,024 bytes)            |  |

| Kbytes/sec.          | kilobyte (1,000 bytes) per second |  |

| kHz                  | kilohertz                         |  |

| kΩ                   | kilohm                            |  |

| Mbyte                | megabyte (1,048,576 bytes)        |  |

| MHz                  | megahertz (1,000 kilohertz)       |  |

| mA                   | milliampere                       |  |

| ms                   | millisecond (1,000 microseconds)  |  |

| ns                   | nanosecond                        |  |

| рV                   | picovolt                          |  |

| V                    | volt                              |  |

| W                    | watt                              |  |

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'n/c' indicates a pin that is a 'no connect'.

#### 4.2 Acronyms

| Acronym | Definition                                 |  |

|---------|--------------------------------------------|--|

| AC      | alternating current                        |  |

| CMOS    | complementary metal-oxide<br>semiconductor |  |

| DC      | direct current                             |  |

| DRAM    | dynamic random-access memory               |  |

| FIFO    | first in/first out                         |  |

| ISA     | industry standard architecture             |  |

| LSB     | least-significant bit                      |  |

| MSB     | most-significant bit                       |  |

| MQFP    | metric quad-flat pack                      |  |

| RAM     | random-access memory                       |  |

| R/W     | read/write                                 |  |

| SDLC    | synchronous data link control              |  |

| TTL     | transistor-transistor logic                |  |

#### Figure 1. Workstation: Printer, Keyboard, Mouse and Modem Ports

Figure 2. Three Serial Ports and One Bidirectional Parallel Port

#### Figure 3. Four Full-Modem Ports

#### 5.0 Pin Information

*Note:* N/C means no connection (make no connections to these pins).

#### 5.1 Pin Functions - Major Operational Modes

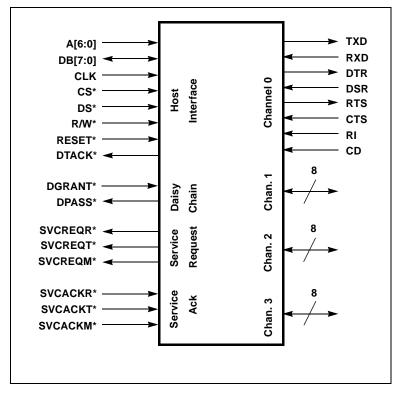

#### Figure 5. Pin Functions — Four Serial Channel Mode

#### Figure 6. Pin Functions — Three Serial/One Parallel Channel Mode

#### 5.2 Pin List

The following naming conventions are used in the pin assignment tables: (\*) after a name denotes an active-low signal. Signal names in parentheses are for the parallel channel.

I = input; I/O = input/output; O = output; OD = open drain.

#### Table 1. General

| Symbol | Pin # | # of Pins | Туре |

|--------|-------|-----------|------|

| RESET* | 79    | 1         | I    |

| CLK    | 73    | 1         | I    |

#### Table 2. Microprocessor Interface

| Symbol  | Pin #                   | # of Pins | Туре |

|---------|-------------------------|-----------|------|

| CS*     | 78                      | 1         | I    |

| DS*     | 77                      | 1         | I    |

| R/W*    | 76                      | 1         | I    |

| DTACK*  | 75                      | 1         | OD   |

| A[6:0]  | 80–83, 85, 87, 89       | 7         | I    |

| DB[7:0] | 93, 95,<br>97–100, 1, 2 | 8         | I/O  |

#### Table 3. Service Request Interface

| Symbol   | Pin # | # of Pins | Туре |

|----------|-------|-----------|------|

| SVCREQR* | 61    | 1         | OD   |

| SVCREQT* | 63    | 1         | OD   |

| SVCREQM* | 65    | 1         | OD   |

| SVCACKR* | 56    | 1         | I    |

| SVCACKT* | 57    | 1         | I    |

| SVCACKM* | 59    | 1         | I    |

| DGRANT*  | 69    | 1         | I    |

| DPASS*   | 71    | 1         | 0    |

#### Table 4. Communication Interface (Sheet 1 of 2)

| Symbol          | Pin # | # of Pins | Туре |

|-----------------|-------|-----------|------|

| TXD0 (PSTROBE*) | 3     | 1         | 0    |

| RXD0 (PACK*)    | 4     | 1         | I    |

| RTS0* (PSLIN*)  | 45    | 1         | 0    |

| CTS0* (PSLCT*)  | 46    | 1         | Ι    |

| DSR0* (PBUSY)   | 47    | 1         | I    |

| DTR0* (PINIT*)  | 43    | 1         | 0    |

| CD0* (PERROR*)  | 49    | 1         | I    |

| RI0* (PPE*)     | 48    | 1         | I    |

| PAUTOFD*        | 53    | 1         | 0    |

| TXD1            | 5     | 1         | 0    |

| RXD1            | 6     | 1         | I    |

| RTS1*           | 36    | 1         | 0    |

| CTS1*           | 38    | 1         | I    |

| DSR1*           | 40    | 1         | I    |

| DTR1*           | 35    | 1         | 0    |

#### Table 4. Communication Interface (Sheet 2 of 2)

| CD1* (PD[2])  | 42 | 1 | I/O |

|---------------|----|---|-----|

| RI1* (PD[3])  | 41 | 1 | I/O |

| TXD2          | 7  | 1 | 0   |

| RXD2          | 9  | 1 | I   |

| RTS2*         | 28 | 1 | 0   |

| CTS2*         | 29 | 1 | I   |

| DSR2*         | 31 | 1 | I   |

| DTR2*         | 27 | 1 | 0   |

| CD2* (PD[4])  | 34 | 1 | I/O |

| RI2* (PD[5])  | 33 | 1 | I/O |

| TXD3          | 11 | 1 | 0   |

| RXD3          | 13 | 1 | I   |

| RTS3*         | 17 | 1 | 0   |

| CTS3*         | 21 | 1 | 0   |

| DSR3*         | 23 | 1 | I   |

| DTR3*         | 15 | 1 | 0   |

| CD3* (PD[16]) | 26 | 1 | I/O |

| RI3* (PD[7])  | 25 | 1 | I/O |

| PD[0]         | 54 | 1 | I/O |

| PD[1]         | 55 | 1 | I/O |

|               |    |   |     |

#### Table 5.Miscellaneous

| Symbol          | Pin #                                                            | # of Pins | Туре |

|-----------------|------------------------------------------------------------------|-----------|------|

| V <sub>CC</sub> | 8, 19, 30, 39, 50, 58,<br>67, 94                                 | 8         | -    |

| GND             | 12, 16, 24, 32, 37, 44,<br>51, 60, 66, 72, 84, 91,<br>96         | 13        | -    |

| NC              | 10, 14, 18, 20, 22, 52,<br>62, 64, 68, 70, 74, 86,<br>88, 90, 92 | 15        | -    |

| Symbol   | Pin No.                    | Туре | Description                                                                                                                                                                                                                                                                                                                               |

|----------|----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET*   | 79                         | I    | <b>ACTIVE-LOW RESET:</b> This pin synchronously resets the CD1400. RESET* must be active for a minimum of 10 system clock cycles. When RESET* is removed, the CD1400 will perform a software initialization of its registers, disable all transmitters and receivers, and when complete, place the firmware revision number in the GFRCR. |

| CLK      | 73                         | I    | <b>CLOCK</b> — <b>SYSTEM CLOCK:</b> The CD1400 requires a nominal 60-MHz clock for proper operation. The system clock is divided by two, internally, to generate all on-chip timing clocks.                                                                                                                                               |

| CS*      | 78                         | I    | <b>CHIP SELECT:</b> When active, CS*, in conjunction with DS*, initiates a host I/O cycle with the CD1400.                                                                                                                                                                                                                                |

| DS*      | 77                         | Ι    | <b>DATA STROBE:</b> During an active I/O cycle, DS* strobes data into on-chip registers during a write cycle or enables data onto the data bus during read cycles.                                                                                                                                                                        |

| R/W*     | 76                         | Ι    | <b>READ/WRITE:</b> R/W* sets the direction of the data transfer between the host and the CD1400. When high, the cycle is a read, and when low, the cycle is a write.                                                                                                                                                                      |

| DTACK*   | 75                         | OD   | <b>DATA TRANSFER ACKNOWLEDGE:</b> When the CD1400 has completed internal operations associated with a host I/O cycle, it activates DTACK* to indicate the end of the cycle. The host may terminate the cycle as soon as DTACK becomes active.                                                                                             |

| A[6:0]   | 80–83,<br>85, 87, 89       | I    | ADDRESS [6:0]: These signals select the on-chip register being accessed during a host I/O cycle.                                                                                                                                                                                                                                          |

| DB[7:0]  | 93, 95,<br>97–100,<br>1, 2 | I/O  | <b>DATA BUS [7:0]:</b> These eight bidirectional signals are the data interface between the host and internal CD1400 registers.                                                                                                                                                                                                           |

| SVCREQR* | 61                         | OD   | <b>SERVICE REQUEST RECEIVE:</b> When the CD1400 needs host service for one of the receivers, it activates this signal.                                                                                                                                                                                                                    |

| SVCREQT* | 63                         | OD   | <b>SERVICE REQUEST TRANSMIT:</b> When the CD1400 needs host service for one of the transmitters, it activates this signal.                                                                                                                                                                                                                |

| SVCREQM* | 65                         | OD   | <b>SERVICE REQUEST MODEM:</b> The CD1400 activates this signal when an enabled change occurs.                                                                                                                                                                                                                                             |

| SVCACKR* | 56                         | I    | <b>SERVICE ACKNOWLEDGE RECEIVE:</b> The host activates this signal to start a receive interrupt service. This is a special-case read cycle, during which the CD1400 places the contents of the Receive Interrupt Vector register on the data bus.                                                                                         |

| SVCACKT* | 57                         | I    | SERVICE ACKNOWLEDGE TRANSMIT: The host activates this signal to start a transmit interrupt service. This is a special-case read cycle, during which the CD1400 places the contents of the Transmit Interrupt Vector register on the data bus.                                                                                             |

| SVCACKM* | 59                         | I    | <b>SERVICE ACKNOWLEDGE MODEM:</b> The host activates this signal to start a modem interrupt service. This is a special-case read cycle, during which the CD1400 places the contents of the Modem Interrupt Vector register on the data bus.                                                                                               |

| DGRANT*  | 69                         | I    | <b>DAISY GRANT:</b> This input, qualified with DS* and a valid service acknowledge (SVCACKR*, SVCACKT*, SVCACKM*), activates the CD1400 service acknowledge cycle.                                                                                                                                                                        |

| DPASS*   | 71                         | 0    | <b>DAISY PASS:</b> This output is driven low when no valid service request exists for the type of service acknowledge active. In multiple-CD1400 designs, this signal is normally connected to the following CD1400 DGRANT* input, forming a service acknowledge daisy chain.                                                             |

| TxD[3:0] | 11, 7, 5, 3                | 0    | <b>TRANSMIT DATA [3:0]:</b> These output signals provide the serial transmit data stream for all four channels. When Channel 0 is operating in Parallel Mode, TxD0 becomes PSTROBE* (See PSTROBE*).                                                                                                                                       |

#### Table 6. Pin Descriptions (Sheet 1 of 3)

| int <sub>el</sub> .                                                         |  |

|-----------------------------------------------------------------------------|--|

| on                                                                          |  |

| arry the serial bit 6 bit streams into the parallel operation, RxD0 becomes |  |

| Table 6. | Pin Desc | riptions | (Sheet 2 of 3) |

|----------|----------|----------|----------------|

|----------|----------|----------|----------------|

| RTS[3:0]*       17<br>36         CTS[3:0]*       21<br>38         DSR[3:0]*       23<br>40         DSR[3:0]*       23<br>40         DTR[3:0]*       15<br>35         CD[3:0]*       15<br>35         CD[3:0]*       40         PD[6],PD[4],<br>PD[2]       26<br>42         PERROR*       26         RI[3:0]*       26 | 3, 9, 4         7, 28, 6, 45         1, 29, 8, 46         3, 31, 0, 47         5, 27, 5, 43 | <br>0<br> <br> <br> | <ul> <li>RECEIVE DATA [3:0]: These input signals carry the serial bit 6 bit streams into the CD1400. When Channel 0 is programmed for parallel operation, RxD0 becomes PACK* (See PACK*).</li> <li>REQUEST TO SEND [3:0]: The request to send output 3 from each channel. These signals are controlled by the Modem Signal Value register 1 inside the CD1400. RTS0* serves a dual-purpose based on the mode of operation of Channel 0 (see PSLIN*).</li> <li>CLEAR TO SEND [3:0]: These are the clear-to-send inputs for each of the channels. If enabled, this signal can control the transmitter, enabling transmission when active, disabling transmission when inactive. CTS0* serves a dual-purpose based on the mode of operation Channel 0 (see PSLCT*).</li> <li>DATA SET READY [3:0]: Data Set Ready for each channel. DSR0* serves a dual-purpose based on the mode of operation of Channel 0 (see PBUSY).</li> </ul> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTS[3:0]*     36       CTS[3:0]*     21       DSR[3:0]*     23       DSR[3:0]*     40       DTR[3:0]*     15       CD[3:0]*     15       PD[6],PD[4],     26       PD[2]     42       PERROR*     RI[3:0]*                                                                                                             | 6, 45<br>1, 29,<br>8, 46<br>3, 31,<br>0, 47<br>5, 27,                                       | 1                   | signals are controlled by the Modem Signal Value register 1 inside the CD1400.<br>RTS0* serves a dual-purpose based on the mode of operation of Channel 0 (see PSLIN*).<br>CLEAR TO SEND [3:0]: These are the clear-to-send inputs for each of the channels. If enabled, this signal can control the transmitter, enabling transmission when active, disabling transmission when inactive. CTS0* serves a dual-purpose based on the mode of operation Channel 0 (see PSLCT*).<br>DATA SET READY [3:0]: Data Set Ready for each channel. DSR0* serves a dual-                                                                                                                                                                                                                                                                                                                                                                     |

| CTS[3:0]*     38       DSR[3:0]*     23       DTR[3:0]*     40       DTR[3:0]*     15       CD[3:0]*     35       CD[3:0]*     26       PD[6],PD[4],     26       PD[2]     42       PERROR*     RI[3:0]*                                                                                                              | 8, 46<br>3, 31,<br>0, 47<br>5, 27,                                                          |                     | channels. If enabled, this signal can control the transmitter, enabling transmission when active, disabling transmission when inactive. CTS0* serves a dual-purpose based on the mode of operation Channel 0 (see PSLCT*).<br><b>DATA SET READY [3:0]:</b> Data Set Ready for each channel. DSR0* serves a dual-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D3R[3:0]     40       DTR[3:0]*     15       CD[3:0]*     35       CD[3:0]*     26       PD[6],PD[4],     26       PD[2]     42       PERROR*     81[3:0]*                                                                                                                                                             | 0, 47<br>5, 27,                                                                             |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DTR[3:0]         35           CD[3:0]*         26           PD[6],PD[4],         26           PD[2]         42           PERROR*         81[3:0]*                                                                                                                                                                      |                                                                                             | 0                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PD[6],PD[4], 26<br>PD[2] 42<br>PERROR*<br>RI[3:0]*                                                                                                                                                                                                                                                                     |                                                                                             | -                   | <b>DATA TERMINAL READY [3:0]:</b> Data Terminal Ready for each channel. These signals are controlled by Modem Signal Value register 2. DTR0* serves a dual-purpose based on the mode of operation of Channel (see PINIT*).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PERROR*                                                                                                                                                                                                                                                                                                                | 6, 34,<br>2, 49                                                                             | I                   | <b>CARRIER DETECT [3:0]:</b> These are Carrier Detects for each PD[6] and PD[4] channel and can be monitored via the Modem Signal Value registers.<br>CD0* serves a dual-purpose based on the mode of operation of Channel 0 (see PERROR*).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                        |                                                                                             |                     | CD1*, CD2* and CD3* serve dual purposes as Parallel Data bits 2, 4, and 6 (PD[2], PD[4] and PD[6]) when Channel 0 is operating in Parallel mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                        | 5, 33,<br>1, 48                                                                             | I                   | <b>RING INDICATOR [3:0]:</b> These are the Ring Indicators for each channel and can be monitored via the Modern Signal Value registers. RI0* serves a dual purpose based on the mode of operation of Channel 0 (see PPE*). RI1*, RI2*, and RI3* serve dual purposes as Parallel Data bits 3, 5, and 7 (PD[3], PD[5], and PD[7]) when Channel 0 is operating in Parallel mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PSTROBE*                                                                                                                                                                                                                                                                                                               | 3                                                                                           | 0                   | <b>PRINTER STROBE:</b> This is the alternate function for TxD0 when Channel 0 is programmed as a parallel port. When the port is selected for output (printer), PSTROBE* is driven active by the CD1400 after a proper data setup time. Data is held for a proper hold time after PSTROBE* is deactivated. When Channel 0 is programmed as an input (scanner) port, PSTROBE* acts as the acknowledge pin to signal completion of data reception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PACK*                                                                                                                                                                                                                                                                                                                  | 4                                                                                           | I                   | <b>PRINTER ACKNOWLEDGE:</b> This is the alternate function of RxD0 when Channel 0 is progr†ammed as a parallel port. When the port is selected as output (printer), this signal is used by the CD1400 to indicate completion of data reception by the printer, and that the next I/O cycle can begin. When Channel 0 is selected as an input (scanner), PACK* is treated as the strobe input. Proper data setup and hold times are required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PSLIN*                                                                                                                                                                                                                                                                                                                 | 45                                                                                          | 0                   | PRINTER SELECT IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PINIT*                                                                                                                                                                                                                                                                                                                 | 43                                                                                          | 0                   | PRINTER INITIALIZE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PAUTOFD*                                                                                                                                                                                                                                                                                                               | 53                                                                                          | 0                   | <b>PRINTER AUTOFEED:</b><br>These three signals are general-purpose outputs. Their state is controlled by the lower three bits of the PSVR (see the register descriptions for detailed information on register bit assignments). PSLIN* and PINIT* are alternate functions for RTS0* and DTR0*, depending on the mode of operation on Channel 0. PAUTOFD* is a single-function output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PSLCT* 4                                                                                                                                                                                                                                                                                                               |                                                                                             |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PPE*                                                                                                                                                                                                                                                                                                                   | 46                                                                                          | I                   | PRINTER SELECT 0 = latch, 1 = buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Symbol  | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERROR* | 49      | I    | <b>PRINTER ERROR:</b><br>These three signals are general-purpose inputs. Their state can be monitored via the upper four bits of the PSVR. As with their modem input counterparts (CTS0*, RI0*, and CD0*), a change in state can be programmed to generate SVCREQM*. The function of these signals is selected automatically based on the mode of operation programmed for Channel 0.<br>If PSLCT* input is at logic '0', the parallel port operates as a latch. The falling edge of the strobe input latches the data. If PSLCT* is logic '1', the input port is a buffer. |

| PBUSY   | 47      | I/O  | <b>PRINTER BUSY:</b> PBUSY is a bidirectional signal; it is an input when transmit is enabled and an output when receive is enabled. During receive data operations, the CD1400 drives PBUSY active after receiving the strobe from the remote. When the device has taken the data, it deasserts PBUSY and activates PACK*. During transmit data operations, the state of PBUSY is made available to the host via the PSVR; however, it does not affect transfer operation and is not a handshake signal for this direction.                                                |

| PD[0]   | 54      | I/O  | <b>PARALLEL DATA BIT:</b> When Channel 0 is operating in Parallel mode, this pin provides the Parallel Data bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PD[1]   | 55      | I/O  | <b>PARALLEL DATA BIT:</b> When Channel 0 is operating in Parallel mode, this pin provides the Parallel Data bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 6.Pin Descriptions (Sheet 3 of 3)

#### 6.0 Registers

All communication with the CD1400 occurs through a large array of registers. Registers are divided into three types:

- Global affect all channels within the device and are always available for host access; access to the local registers of a particular channel requires selecting the register set of that channel.

- Virtual are only available to the host during the context of a service routine.

- Per-channel pertain only to the channel being referenced.

There are four sets of per-channel registers, one for each channel. Selection of the register set is accomplished by writing the Channel Number (0 through 3) into the Channel Access Register (CAR). This causes a 'bank switch' action, allowing the registers of the selected channel to be accessed. At any given time, only the registers of a single channel are available. Once selected, this register set remains available until the CAR is changed by the host.

The tables on the following pages define the register symbols, names, read and write access modes, and the internal offset address for each register in the CD1400. The offset address is applied to the address bus (A[6:0]) during a host I/O cycle to select a particular register. A detailed description of the host interface is presented in "Host Interface" on page 30.

In the register bit definitions immediately following the register tables, some registers are shown with two functions. In these cases, the first definition applies to the Serial Operation Mode of Channel 0, and the second to Parallel Mode. For Channels 1 through 3, only the function labeled 'Serial' applies.

"Programming" on page 71 presents a detailed description of register programming.

Note that the addresses are shown relative to the CD1400 definition of the address lines. In 16- and 32-bit systems, it is a common practice to connect 8-bit peripherals to only one byte lane. Thus, in 16-bit systems, the CD1400 appears at every other address; for example, the CD1400 A0 is connected to the host A1. In 32-bit systems, the CD1400 appears at every fourth address; (the CD1400 A0 is connected to the host A2). In either of these cases, the addresses used by the programmer will be different than what is shown.

For instance, in a 16-bit Motorola 68000-based system, the CD1400 is placed on data lines D0-D7, which are at odd addresses in the Motorola manner of addressing. The CD1400 A0 is connected to the 68000 A1 and so on. Thus, CD1400 address x'40 becomes x'81 to the programmer. It is 'left-shifted' 1 bit, and A0 must be '1' for low-byte (D0-D7) accesses.

#### 6.1 CD1400 Register Map

#### Table 7. Global Registers

| Name  | Description                            | Addr.<br>Mode | INT | Size | Access | Page |

|-------|----------------------------------------|---------------|-----|------|--------|------|

| GFRCR | Global Firmware Revision Code Register | G             | 40  | В    | R/W    | 88   |

| CAR   | Channel Access Register                | G             | 68  | В    | R/W    | 88   |

| GCR   | Global Configuration Register          | G             | 4B  | В    | R/W    | 89   |

| SVRR  | Service Request Register               | G             | 67  | В    | R      | 90   |

| RICR  | Receive Interrupting Channel Register  | G             | 44  | В    | R/W    | 90   |

| TICR  | Transmit Interrupting Channel Register | G             | 45  | В    | R/W    | 90   |

| MICR  | Modem Interrupting Channel Register    | G             | 46  | В    | R/W    | 91   |

| RIR   | Receive Interrupt Register             | G             | 6B  | В    | R/W    | 92   |

| TIR   | Transmit Interrupt Register            | G             | 6A  | В    | R/W    | 92   |

| MIR   | Modem Interrupt Register               | G             | 69  | В    | R/W    | 92   |

| PPR   | Prescaler Period Register              | G             | 7E  | В    | R/W    | 93   |

#### Table 8. Virtual Registers

| Name                                                                                                                                              | Description                        | Addr.<br>Mode | INT | Size | Access | Page |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------|-----|------|--------|------|--|

| RIVR                                                                                                                                              | Receive Interrupt Vector Register  | G             | 43  | В    | R      | 94   |  |

| TIVR                                                                                                                                              | Transmit Interrupt Vector Register | G             | 42  | В    | R      | 94   |  |

| MIVR                                                                                                                                              | Modem Interrupt Vector Register    | G             | 41  | В    | R      | 95   |  |

| TDR                                                                                                                                               | Transmit Data Register             | G             | 63  | В    | W      | 96   |  |

| RDSR                                                                                                                                              | Receive Data/Status Register       | G             | 62  | В    | R      | 96   |  |

| MISR                                                                                                                                              | Modem Interrupt Status Register    | G             | 4C  | В    | R      | 98   |  |

| EOSRR                                                                                                                                             | End Of Service Request Register    | G             | 60  | В    | W      | 98   |  |

| NOTE: The page numbers shown in these tables indicate the detailed register description locations in "Detailed Register Descriptions" on page 88. |                                    |               |     |      |        |      |  |

#### Table 9. Channel Registers (Sheet 1 of 2)

| Symbol | Register Name                   | Addr.<br>Mode | INT | Size | Access | Page |

|--------|---------------------------------|---------------|-----|------|--------|------|

| LIVR   | Local Interrupt Vector Register | Р             | 18  | В    | R/W    | 99   |

| CCR    | Channel Command Register        | Р             | 05  | В    | R/W    | 99   |

| SRER   | Service Request Enable Register | Р             | 06  | В    | R/W    | 104  |

| COR1   | Channel Option Register 1       | Р             | 08  | В    | R/W    | 105  |

| COR2   | Channel Option Register 2       | Р             | 09  | В    | R/W    | 107  |

| COR3   | Channel Option Register 3       | Р             | 0A  | В    | R/W    | 108  |

| Symbol | Register Name                      | Addr.<br>Mode | INT | Size | Access | Page |

|--------|------------------------------------|---------------|-----|------|--------|------|

| COR4   | Channel Option Register 4          | Р             | 1E  | В    | R/W    | 110  |

| COR5   | Channel Option Register 5          | Р             | 1F  | В    | R/W    | 111  |

| CCSR   | Channel Control Status Register    | Р             | 0B  | В    | R      | 112  |

| RDCR   | Received Data Count Register       | Р             | 0E  | В    | R      | 114  |

| SCHR1  | Special Character Register 1       | Р             | 1A  | В    | R/W    | 116  |

| SCHR2  | Special Character Register 2       | Р             | 1B  | В    | R/W    | 116  |

| SCHR3  | Special Character Register 3       | Р             | 1C  | В    | R/W    | 116  |

| SCHR4  | Special Character Register 4       | Р             | 1D  | В    | R/W    | 117  |

| SCRL   | Special Character Range, Low       | Р             | 22  | В    | R/W    | 117  |

| SCRH   | Special Character Range, High      | Р             | 23  | В    | R/W    | 117  |

| LNC    | LNext Character                    | Р             | 24  | В    | R/W    | 118  |

| MCOR1  | Modem Change Option Register 1     | Р             | 15  | В    | R/W    | 118  |

| MCOR2  | Modem Change Option Register 2     | Р             | 16  | В    | R/W    | 120  |

| RTPR   | Receive Time-out Period Register   | Р             | 21  | В    | R/W    | 121  |

| MSVR1  | Modem Signal Value Register 1      | Р             | 6C  | В    | R/W    | 122  |

| MSVR2  | Modem Signal Value Register 2      | Р             | 6D  | В    | R/W    | 122  |

| PSVR   | Printer Signal Value Register      | Р             | 6F  | В    | R/W    | 122  |

| RBPR   | Receive Baud Rate Period Register  | Р             | 78  | В    | R/W    | 123  |

| RCOR   | Receive Clock Option Register      | Р             | 7C  | В    | R/W    | 124  |

| TBPR   | Transmit Baud Rate Period Register | Р             | 72  | В    | R/W    | 124  |

| TCOR   | Transmit Clock Option Register     | Р             | 76  | В    | R/W    | 125  |

#### Table 9. Channel Registers (Sheet 2 of 2)

#### 6.2 Register Definitions

#### Table 10. Global Registers (Sheet 1 of 2)

|                                                |                  |                | Global F   | Registers    |     |    |     |     |

|------------------------------------------------|------------------|----------------|------------|--------------|-----|----|-----|-----|

| Global Firmware Revision Code Register (GFRCR) |                  |                |            |              |     | В  | R/W | 88  |